AMD's 3D Memory-Extender Speeds Gaming

Samuel K. Moore

IEEE Spectrum

PCs have long come with the option to add more memory, giving extra-large applications and data-heavy work greater speed. Thanks to 3D chip stacking, AMD’s next generation CPU comes with that option, too. It’s not an aftermarket add on, of course, but if you’re looking to build a computer with some extra oomph, ordering up a processor with an extra-large cache memory could be the way to go.

The 3D stacking technique tripled the Zen 3 processor core’s cache memory, speeding its execution of games and electronic design automation. John Wuu AMD senior fellow design engineer detailed the previously announced technology for virtual attendees of the IEEE International Solid State Circuits Conference in February.

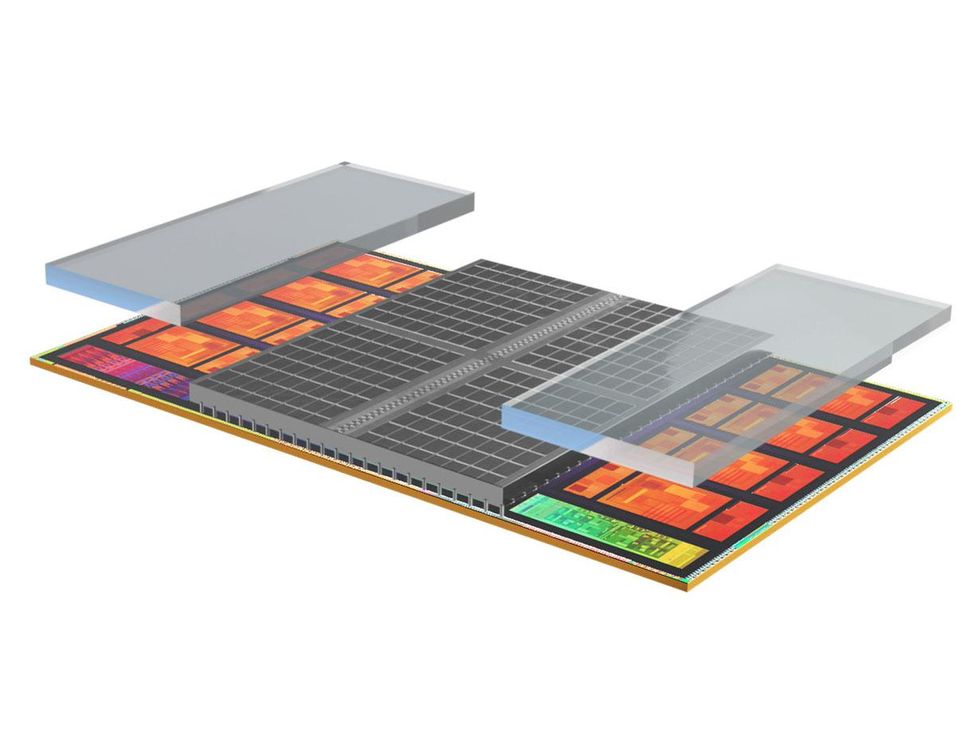

Even though Zen 2 and the new Zen 3 processor cores are both made using the same TSMC manufacturing process (N7)—and therefore have the same size transistors, interconnects, and everything else—AMD made so many architectural alterations that even without the extra cache memory, Zen 3 provides 19 percent performance improvement on average. One of those architectural gems was the inclusion of a set of set of through-silicon vias (TSVs), vertical interconnects that burrow straight down through most of the silicon. The TSVs are built within Zen 3’s highest level cache, blocks of SRAM called L3, which is sits in the middle of the 81-square-millimeter compute chiplet and is shared across all eight of its cores.

In processors destined for data-heavy workloads, the Zen 3 wafer’s back side is thinned down until the TSVs are exposed. Then a 64-megabyte SRAM chiplet is bonded to those exposed TSVs using what’s called hybrid bonding—a process that’s like cold-welding the copper together. The result is a dense set of connections that can be as close together as 9 micrometers. Finally, for structural stability and heat conduction, two blank silicon chiplets are attached to cover the remainder of the Zen 3 CPU die.

Adding the extra memory by setting it beside the CPU die was not an option, because data would take too long to get to the processor cores. “Despite tripling the L3 [cache] size, 3D V-Cache only added four [clock] cycles of latency—something that could only be achieved through 3D stacking,” John Wuu AMD senior fellow design engineer told attendees of the IEEE International Solid State Circuits Conference.

The bigger cache made its mark in high end games. Using the desktop Ryzen CPU with 3D V-Cache sped games rendered at 1080p by an average of 15 percent. It was good for more serious work as well, shortening the runtime for a difficult semiconductor design computations by 66 percent.

The industry’s ability to shrink SRAM is slowing compared to how well it can shrink logic, Wuu pointed out. So you can probably expect future SRAM expansion packs to continue to be made using more established manufacturing processes while the compute chiplets are driven down to Moore’s Law’s bleeding edge.

Continue Reading